Intel Clearwater Forest Xeon processor architecture revealed: up to 17 chips, continuing the design of the I/O part from the previous generation

According to previous reports, Clearwater Forest will be Intel's second-generation high-efficiency core Xeon processor, and as the successor to the first generation product Sierra Forest, it is planned to be launched in 2025. According to sources @ SquashBionic (Bionic Squash), Clearwater Forest will maintain a maximum design of 288 cores. According to the diagram provided by Intel, each basic chip will be equipped with 4 computing chips and connected through Foveros Direct 3D connection.

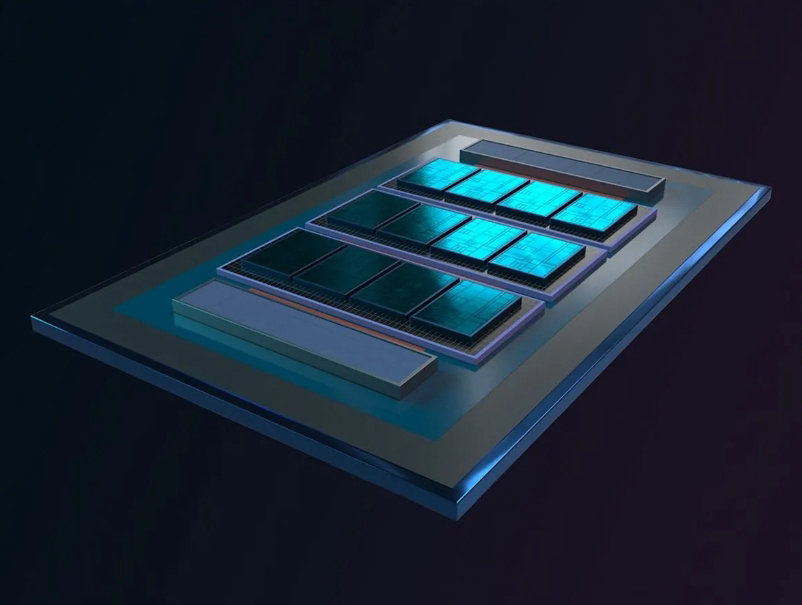

Intel Clearwater Forest Xeon processor schematic diagram

Intel Clearwater Forest Xeon processor schematic diagram

Eric Fetzer, Director of Data Center Technology and Pathfinding at Intel, stated that the non logical parts of the entire chip do not significantly benefit from process improvements. The benefits of using advanced processes in the SRAM cache section of the CPU are lower than those of logic, while the benefits of using high-speed I/O sections are even lower. Considering the yield issue of large chips, Intel chose a design on Clearwater Forest that separates SRAM and high-speed I/O from the logic part.

- Computing chips: up to 12, based on Intel 18A process, including energy-efficient core processor cores;

- Basic chips: up to 3, based on Intel 3 process, including main cache, voltage regulator circuit, and internal network;

- I/O chips: up to 2, based on the Intel 7 process, similar to the I/O chips used on the Sierra Forest and Granite Rapids processors.

Feice also pointed out that the cross chip data transmission energy consumption of Foveros Direct 3D is 0.05 * 10-12 joules per bit, which is equivalent to the internal energy consumption of the chip.

Regarding the 18A process used in the Clearwater Forest computing chip, Fitzer believes that the RibbonFET transistor it uses will bring greater flexibility than existing FinFETs. The performance improvement in transistors is closely related to current, while RibbonFET allows for continuous adjustment by changing the width of the transistor. Unlike FinFET, which requires adjusting the current by changing the number of fins.

Intel RibbonFET Technology Diagram

Scan the code to follow us and get more news and information about the electronic chip industry!

Scan the code to follow us and get more news and information about the electronic chip industry!